An important step in implementing digital designs on an FPGA is determining the number of resources that an FPGA design consumes and evaluating the timing of the final design. This information is important during the design process as it gives feedback on how your SystemVerilog code translates into actual logic resources. It is essential that you review the resources of every design you create. This tutorial summarizes how to determine the resources and timing of your FPGA design.

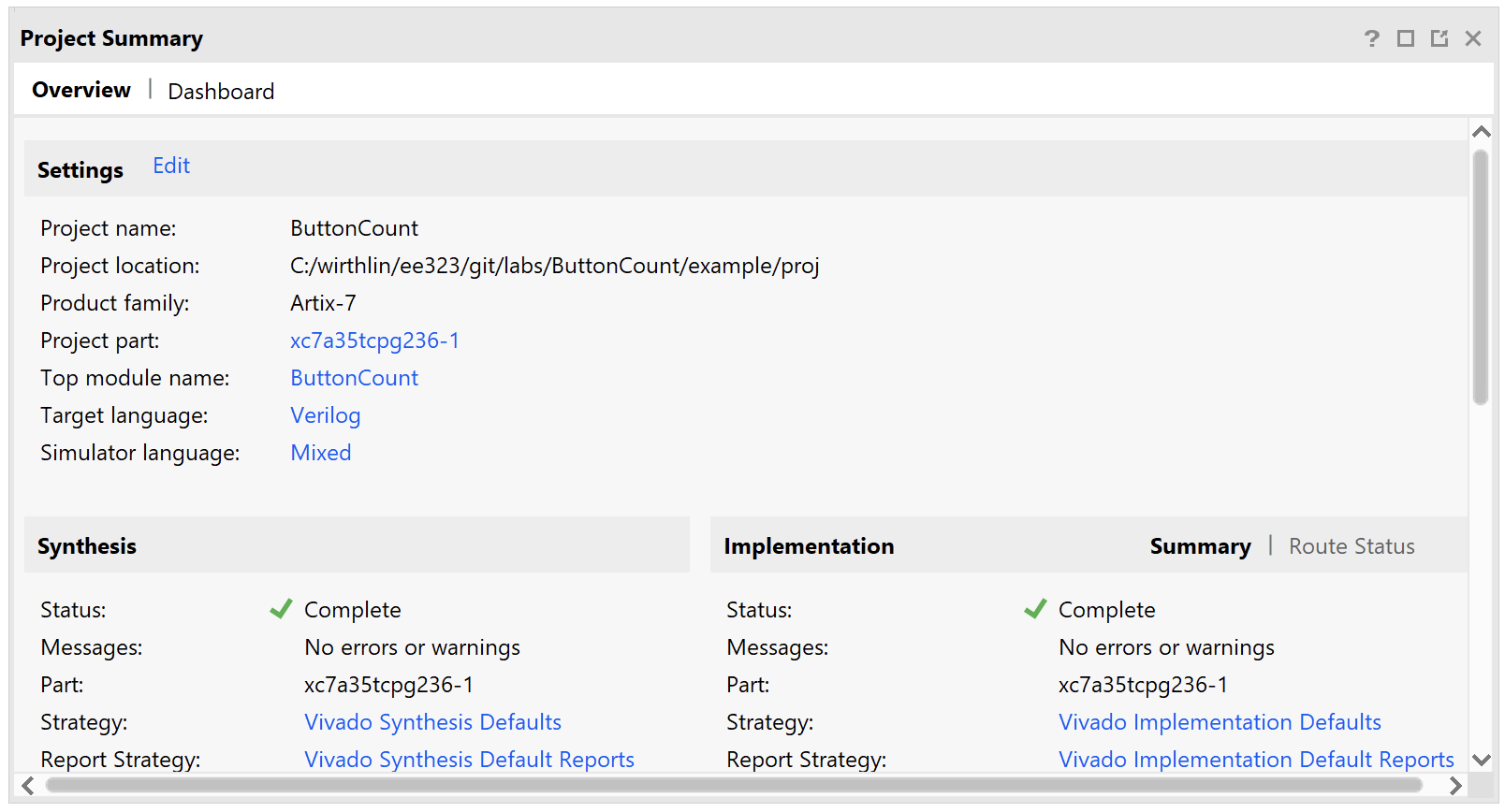

The design utilization can be found in the “Project Summary” Pane in the Vivado project manager as shown in the image below.

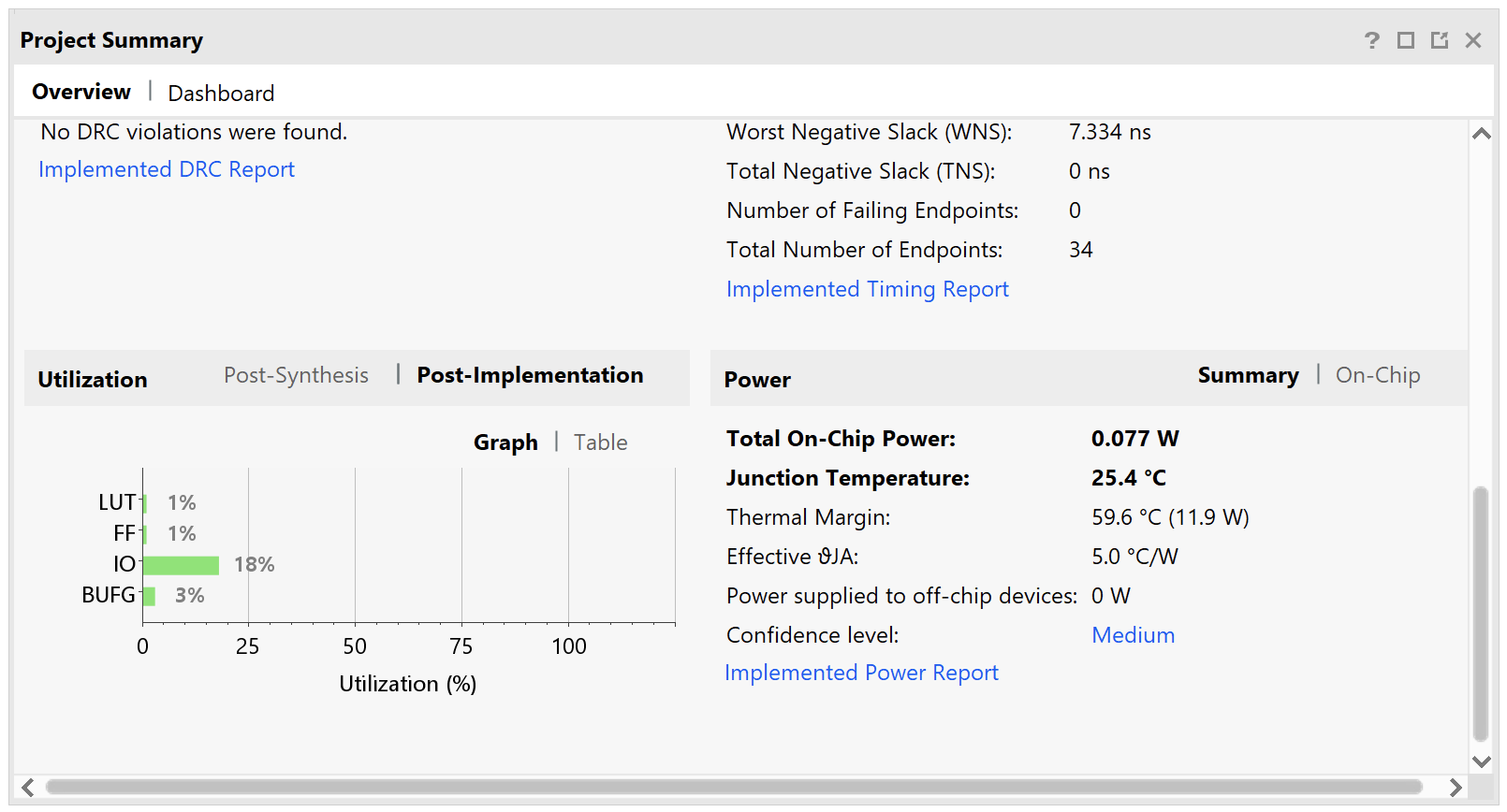

This pane has a lot of information in it and since the utilization information is listed at the bottom of this pane it may not show up when you first review the pane. Scroll down to the bottom of this pane as shown below. The timing number you are most interested in is “Worst Negative Slack” (WNS). In this example, WNS is 7.334 ns. This says that there is an extra 7.334 ns out of the 10 ns clock period available in the system suggesting that this circuit could operate much faster than 100 MHz. Designs with a lot of logic will have a lower WNS. If WNS is negative then the design will not operate at the given clock rate. It is essential that you review this number to make sure your circuit will operate at the given clock rate.

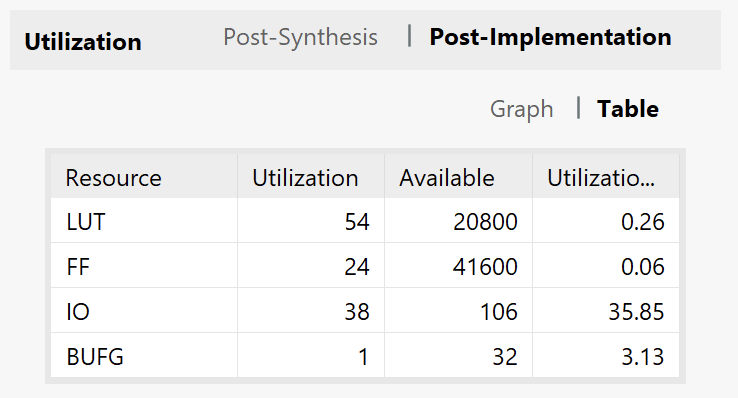

The “Utilization” widget in the bottom left of this pane shows the utiliation, in percentage, of the resources of the FPGA. The utilization percentage is not as interesting as the actual utilization. Click on the words “Table” in the graph to switch to table view. he results are shown in the image below. This example indicates that the design consumes 54 “Look up Tables” (or LUTs), 24 Flip-FLops (FFs), 38 Input/Output pins (IO), and 1 global clock buffer (BUFG). As shown in this table, the FPGA contains a large number of these resources and this particular design consumes a very small amount of logic resources.

It is possible to estimate the resources of the design before completing the implementation step. If you click on the “Post-Synthesis” text in the Utilization widget, you will see the estimated utilization after completing the synthesis step but before the full implementation step.