Table of Contents

The Vivado design suite has a professional logic simulation tool that you can use to simulate the behavior of your SystemVerilog HDL files. HDL Simulation tools like this are used by professional engineers to simulate very complex and large digital design files. Your ability to use simulation tools effectively is key to successfully designing digital circuits. This tutorial will guide you through how to setup and start the Vivado simulation tool. Other tutorials are available that describe how to run your simulation once it is properly setup.

Set “Top” Module

The Vivado simulator is able to simulate any of the SystemVerilog files that are part of your project. Before simulating, you need to identify the SystemVerilog module you want to simulate. The module that is simulated is called the “top” module. You can set the “top” module under Simulation Sources as follows:

- In the Project Manager, in the Sources pane, expand the Simulation Sources folder and the folder inside of that.

- Right click on the source you want to set as top module, then click Set as Top. If your file is already set as the top it will have a small hierarchy picture next to the filename and the Set as Top option will not be available.

Remove default simulation run time

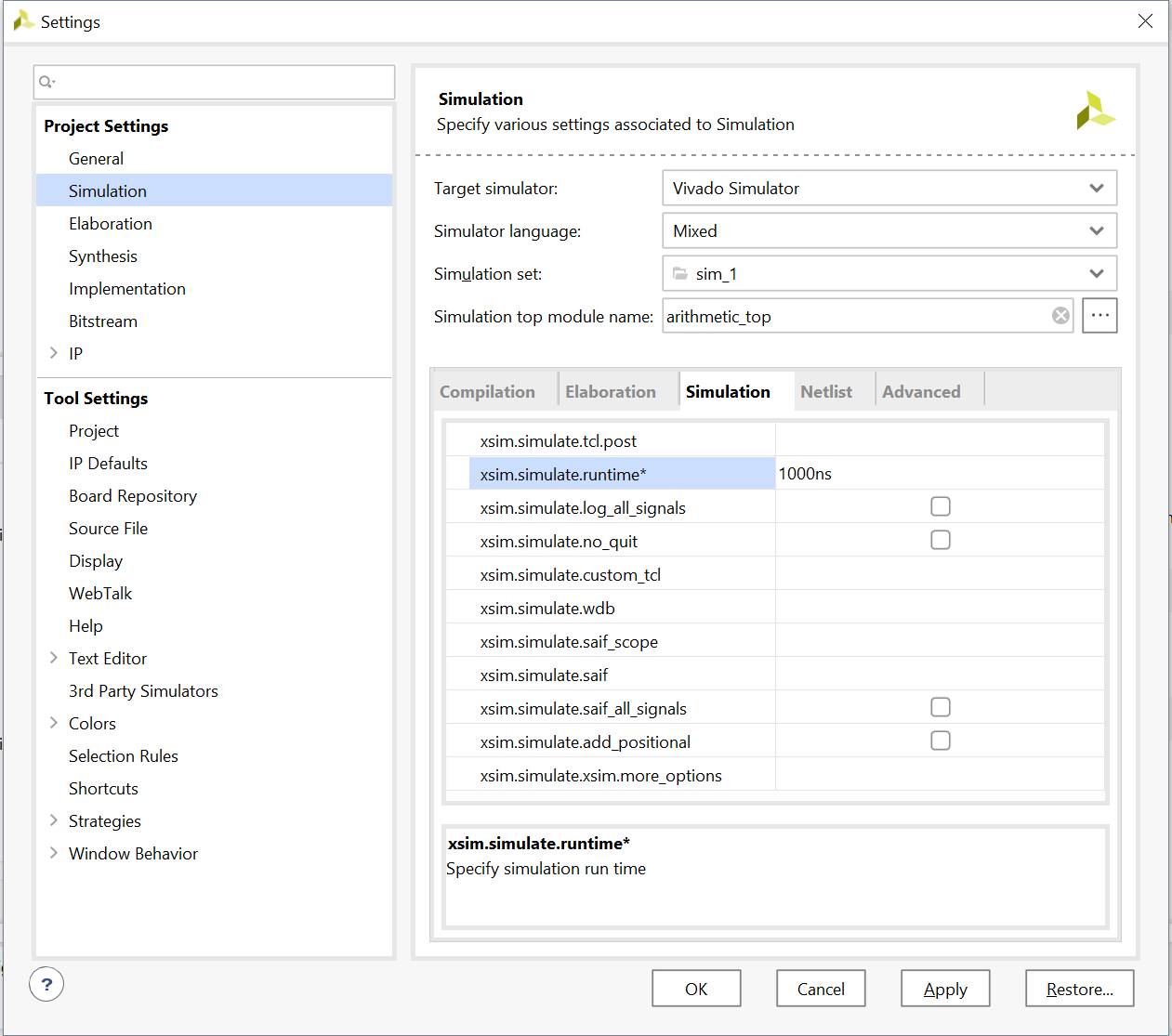

By default, the simulator will simulate 1000 ns of time when the simulation is first run. This is not helpful as the inputs to the simulation are not yet set. It is best to remove this default simulation run time before starting the simulation (you only need to do this once - this will be saved in your project settings). Follow these steps to remove the default simulation run time:

- Right-Click the SIMULATION link in Flow Navigator and click Simulation Settings….

- Click the Simulation Tab in the middle of the window that pops up.

- Click the small x to the right of Simulation Run Time. This should remove the 1000ns if it is there, which it is by default.

- Click OK.

Run Simulation

At this point you can start the simulation tool:

- Click Run Simulation

- Click Run Behavioral Simulation.

The simulator will perform an “elaboration” step on your SystemVerilog code before starting the simulation. During elaboration, the simulator may find errors in your SystemVerilog code that were not found by the syntax checker. If you have errors, resolve them and re-run the simulation.

A video example of performing these steps is shown below:

Simulation GUI Overview

The following video provides a summary of running the Vivado simulation. Watch this video as you complete your simulation.

BEWARE OF THE SIMULATOR DEMONS !!!

Our experience has been that the simulator sometimes gets in a funny state, meaning that you may think you have changed and then re-compiled your circuit but the simulator doesn’t realize this. It happens to every student one or more times in the semester

If the simulator just seems to not be reflecting your circuit changes or not working at all, you need to take action to reset it. There is a whole webpage devoted to this. It is called Taming Vivado and is under the “Resources” link in the sidebar of this webpage. When this happens consult that page - it will lead you through the steps needed to kill the simulator demons and get it working again.